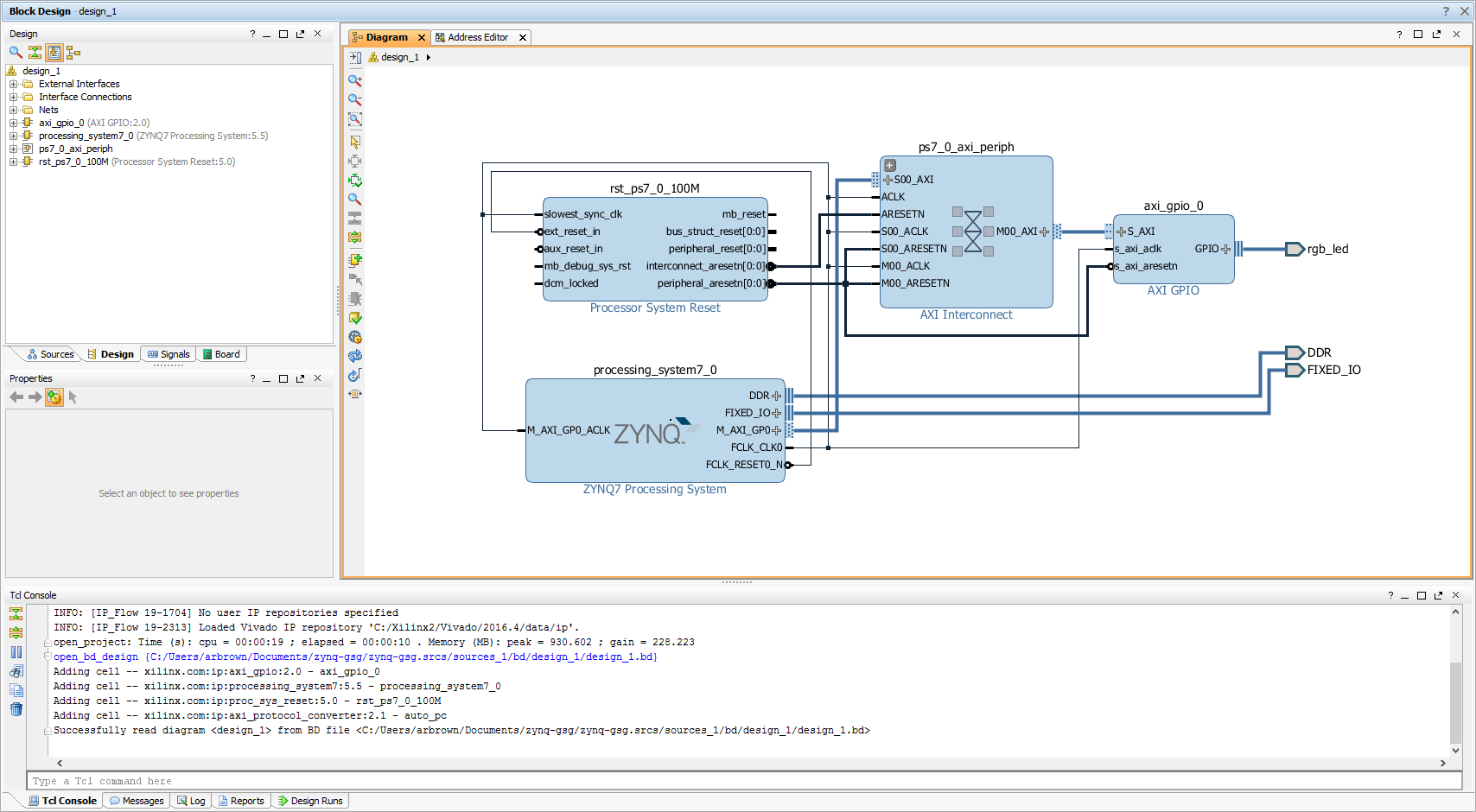

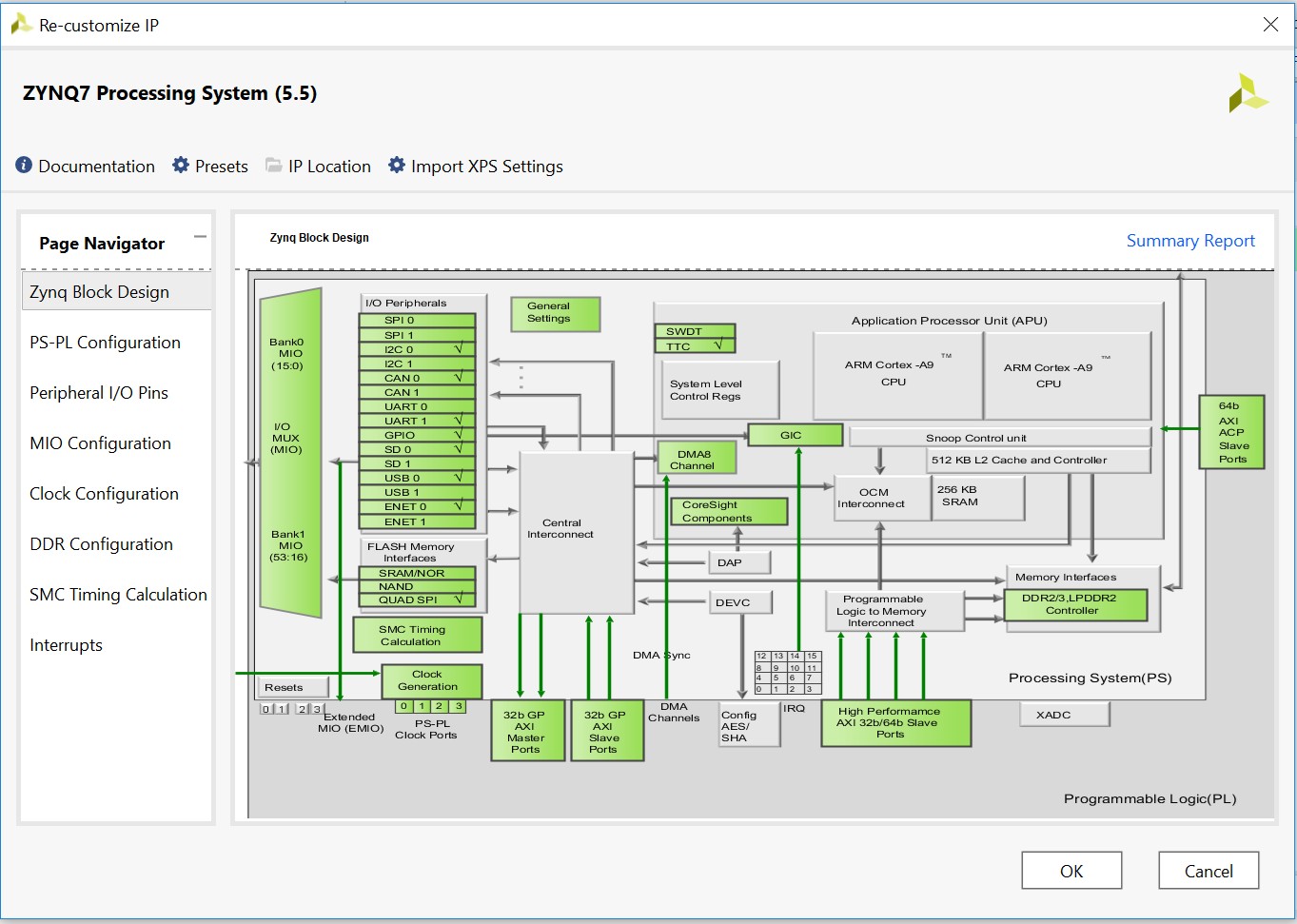

verilog - In Vivado, how to "Create Port" in a "Block Design" that is mapped to a "Board Definition File" port for PicoZed - Stack Overflow

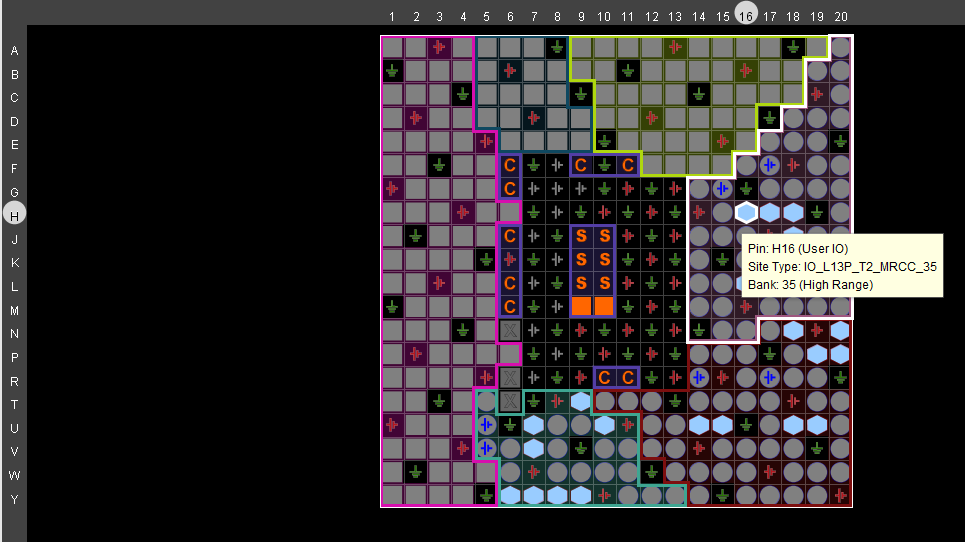

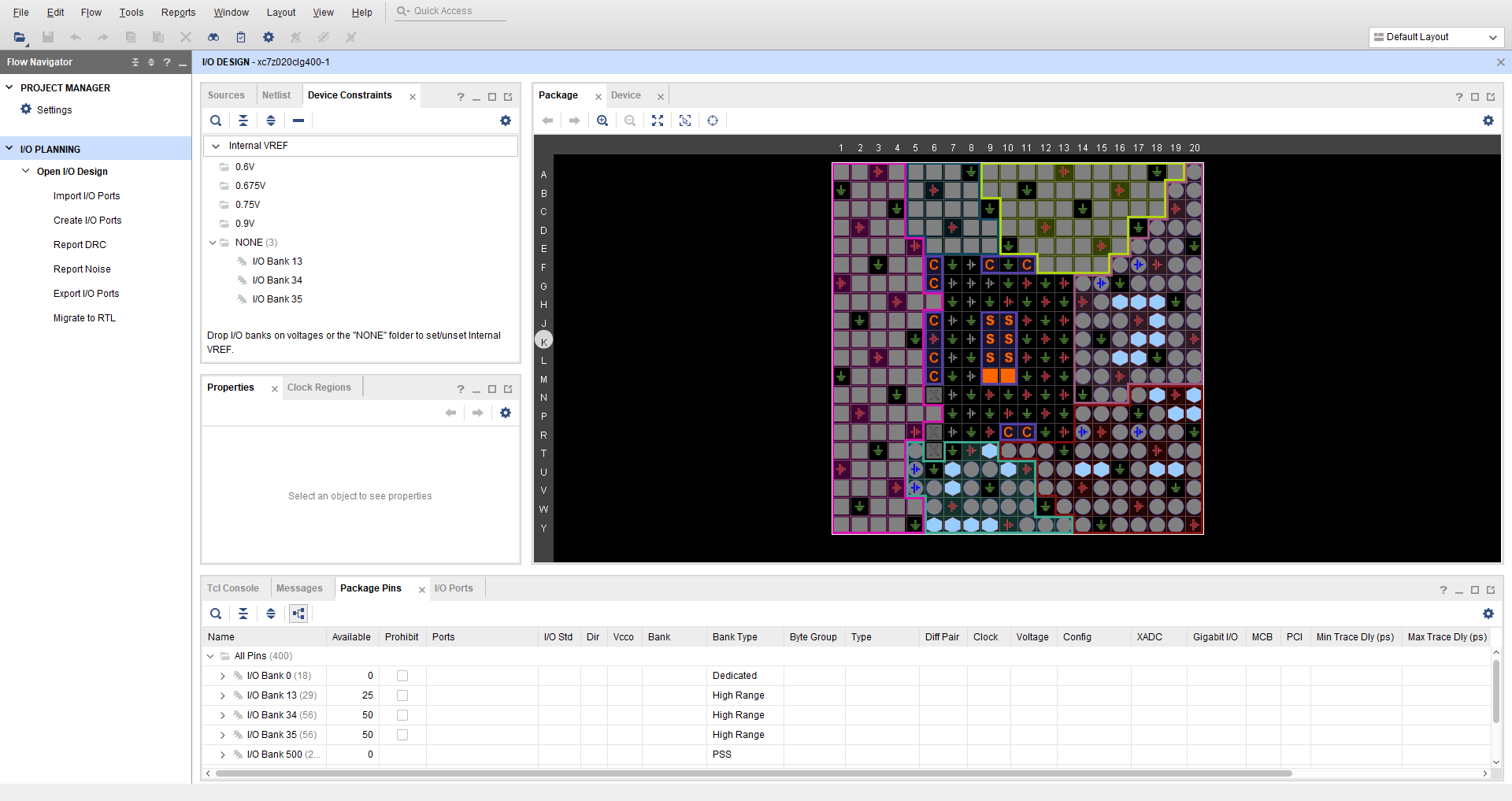

56354 - Vivado write_bitstream - ERROR: [Drc 23-20] Rule violation (NSTD-1) Unspecified I/O Standard - X out of Y logical ports use I/O standard (IOSTANDARD) value 'DEFAULT', instead of a user assigned specific value